An FPGA-Based Processing Pipeline for High Definition Stereo Video

This paper presents a real-time processing platform for high-definition stereo video.

November 4, 2011

EURASIP Journal on Image and Video Processing (EURASIP JIVP) 2011

Authors

Pierre Greisen (Disney Research/ETH Joint PhD)

Simon Heinzle (Disney Research)

Markus Gross (Disney Research/ETH Zurich)

Andreas Burg (EPF Lausanne)

An FPGA-Based Processing Pipeline for High Definition Stereo Video

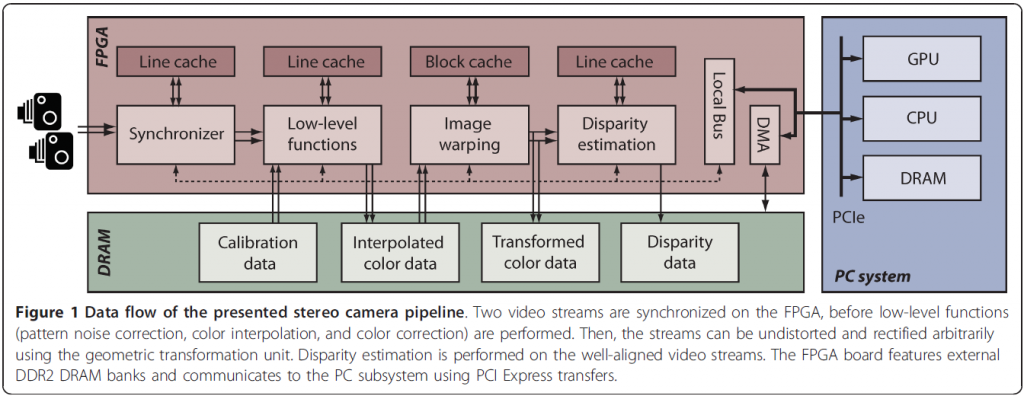

The system is capable to process stereo video streams at resolutions up to 1, 920 × 1, 080 at 30 frames per second (1080p30). In the hybrid FPGA-GPU-CPU system, a high-density FPGA is used not only to perform the low-level image processing tasks such as color interpolation and cross-image color correction, but also to carry out radial undistortion, image rectification, and disparity estimation. We show how the corresponding algorithms can be implemented very efficiently in programmable hardware, relieving the GPU from the burden of these tasks. Our FPGA implementation results are compared with corresponding GPU implementations and with other implementations reported in the literature.